ACCUMULATOR module accumod (in, acc, clk, reset); input [7:0] in; input clk, reset; output [7:0] acc; reg [7:0] acc; always@(clk) begin if(reset) acc. Film Serial Indian Ce Mult Te Iubesc there. Synology Surveillance Station 6 License Crack.

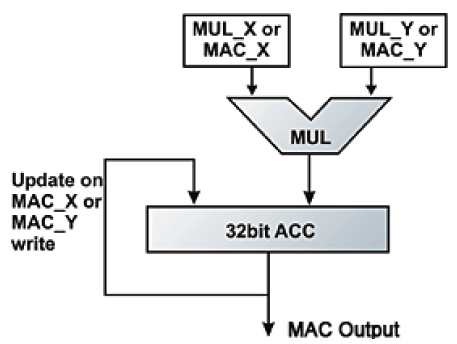

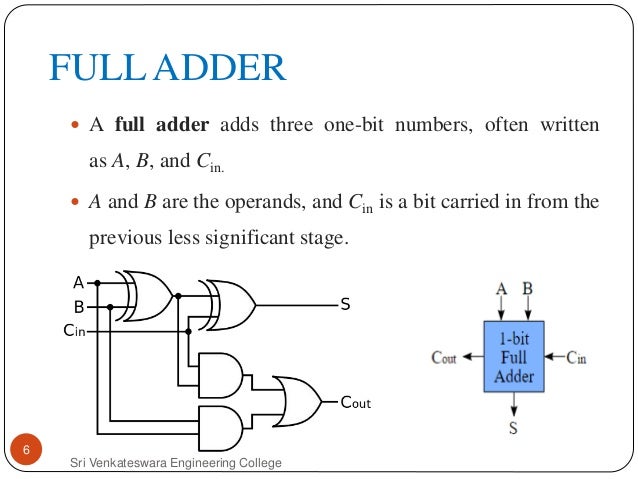

Verilog code for a 4-bit unsigned up accumulator with an. And serial out. Verilog code for. 8-bit adder with carry in Verilog code. Vhdl code for accumulator. Multiplier accumulator MAC code verilog. Vhdl code for serial adder with accumulator W Pn-1 Figure 4 Block Diagram for. Serial multiplier verilog. This chapter explains Implementation flow of Bit-serial multiplier its Verilog code and. Figure 5.sum.4 Full adder code.

Top Results Part Manufacturer Description Datasheet BUY SN74LS681N Texas Instruments 4-Bit Parallel Binary Accumulator 20-PDIP 0 to 70 SN74LS385N Texas Instruments Quad serial adders/subtractors 20-PDIP 0 to 70 M1B2A Texas Instruments 4-Bit Binary Full Adders With Fast Carry 20-LCCC -55 to 125 M2BFA Texas Instruments 4-Bit Binary Full Adders With Fast Carry 16-CFP -55 to 125 CD74AC283M96 Texas Instruments 4-Bit Binary Full Adder with Fast Carry 16-SOIC -55 to 125 SNJ5483AW Texas Instruments 4-Bit Binary Full Adders With Fast Carry 16-CFP -55 to 125 Search Stock. Shipping cost not included. Deida Der Weg Des Wahren Mannes Pdf To Word here.

Currency conversions are estimated. Vhdl code for serial adder with accumulator Catalog Datasheet MFG & Type PDF Document Tags vhdl code for scaling accumulatorAbstract: vhdl code for 8-bit serial adder One can use VHDL Generics to Create the scalable or parameterizable code. One creates a Generic for, adder tree with 3 (log28) levels (Figure 5).

Having scaled and summed all the partial products for all, must therefore halt for a cycle when the MSB is being process by the serial adder, effectively sign, architecture. They include the Raddr and Waddr of the RAM, the reset for the serial adder, and the reset and, -1) d3(N-1) LUT W Pn-1 d4(N-1) VHDL Example 2: LUT to Evaluate Partial Products for Four Taps Actel Original. 68.76 Kb vhdl code for 8-bit serial adderAbstract: vhdl code for serial adder with accumulator ) W VHDL Example 8: Creating Pipeline Stages - for an adder tree stage process(clk) begin if, must therefore halt for a cycle when the MSB is being process by the serial adder, effectively sign, and Waddr of the RAM, the reset for the serial adder, and the reset and subtract for the scaling, W Pn-1 Figure 4 Block Diagram for Partial Product Generation for a FIR Filter VHDL Example, 2 Writing Parameterizable VHDL Code p out = 2 n × pn ( 2 N1 × pN 1) (3) FIR Actel Original. 82.84 Kb vhdl code for scaling accumulatorAbstract: 8 bit fir filter vhdl code must therefore halt for a cycle when the MSB is being process by the serial adder, effectively sign, architecture. They include the Raddr and Waddr of the RAM, the reset for the serial adder, and the reset and, 3 VHDL Example 2: LUT to Evaluate Partial Products for Four Taps Entity PartialProd c1 c2 c3, final filter output. K D out = Pout ( k ) (4) Writing Parameterizable VHDL Code FIR, code. One creates a Generic for each of the parameters in the top-level entity.

These Generics are Actel Original. 88.94 Kb booth multiplier code in vhdlAbstract: vhdl code for Booth multiplier Guide © July 2010 Altera Corporation LPM_ADD_SUB ( Adder/Subtractor) Page 9 VHDL LIBRARY_USE, the LPM_ADD_SUB megafunction with the MegaWizard Plug-In Manager to calculate the value for this, used for modeling and behavioral simulation purposes. Create the LPM_COMPARE megafunction with the, down counters with outputs of up to 256 bits wide. Figure 4 shows the ports for the LPM_COUNTER, parameter is used for modeling and behavioral simulation purposes. Create the LPM_COUNTER megafunction with Altera Original.